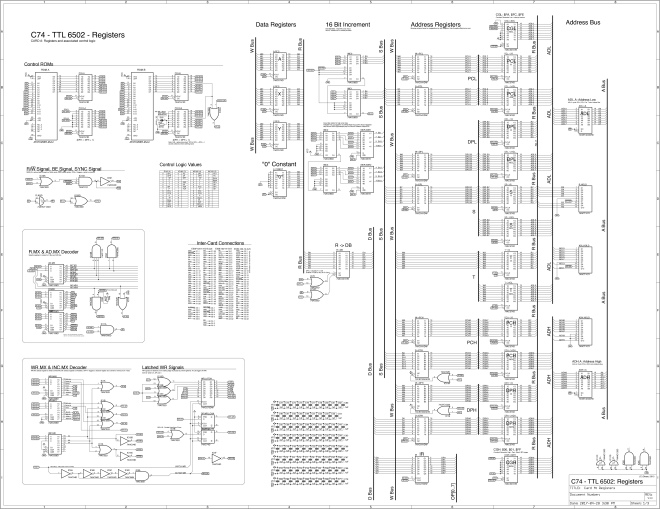

Card A holds the CPU Registers and main busses. Schematics coordinates in the descriptions below are shown as “(P.RC)”, for Page, Row and Column, e.g. “(1.A1)”. The schematic image below can be opened in a separate window to zoom-in as required and follow along.

NOTE: The original prototype boards described below were patched during debugging. Please see the Project Files in the Internals page for details on these patches.

Datapath

The datapath of the C74-6502 consists mainly of a “write bus” (W-Bus) to write to internal 8-bit registers, and a common “read bus” (R-Bus) to read from them. The ALU takes input from registers via the R-Bus and outputs its result onto the W-Bus, to be written back to registers. Registers are all 8-bits wide, with address registers being paired to form 16-bit quantities as necessary. There are also a few special purpose registers, constant generators, and the Instruction Register, as follows:

- 8-Bit Data Registers: A, X and Y

- 16-Bit Address Registers: Program Counter (PCL/PCH), Data Pointer (DPL/DPH)

- 8-Bit Address Registers: Stack Pointer (SP), Temporary Register (T)

- 16-Bit Address Constants: Constant Generator (CGL/CGH)

- 8-Bit Data Constants: Zero Constant (STZ), Bitwise Constant Generator (BCG)

- 8-Bit Instruction Register: IR

- 8-Bit Special Purpose Registers: A&H, DPH+1 (see C74-6502 Undocumented Opcodes)

The CPU has an internal data bus (D-Bus) and an internal address bus (ADL/ADH). Tri-state buffers connect these to the external Data Bus (DB) and the external Address Bus (A-Bus) respectively. The D-Bus takes values from Registers via the R-Bus during writes to memory, and places values on the W-Bus during reads from memory. Address registers and constants can be selectively output-enabled onto the ADL/ADH busses (as required by the addressing mode in effect) to drive the External Address Bus (A-Bus).

A dedicated 16-bit Address Incrementer takes the current address from ADL/ADH and delivers its output back to specific address register through the 16-bit wide Sum Bus (S-Bus).

Data Registers A, X, Y, STZ Constant Generator

The A, X, and Y Data Registers (1.A4) take input from the W-Bus and output directly on to the R-Bus. Each register has an active-low output enable signal (/A.R, /X.R and /Y.R), and an edge-triggered write signal (A.WR, X.WR and Y.WR). The STZ Zero Constant Generator (1.D4) is a simple buffer with its inputs tied to ground. It has /STZ.R as its active-low output enable signal.

16-Bit Incrementer (INC16)

The 16-bit Address Incrementer (1.A5) operates independently of the main ALU. Using a dedicated 16-Bit incrementer allows addresses to be incremented during cycles when the ALU and W-Bus are otherwise busy (for example, when incrementing PC while at the same time storing a value into a register).

The low-byte of the incrementer uses a standard ripple-carry configuration, while the high-byte uses a Skip Adder. (The Skip Adder is one of several optimizations used in the C74-6502 to meet its target clock speed).

The Incrementer takes input from the ADL/ADH internal address bus, and delivers its output to the 16-bit S-Bus (Sum Bus). “.WS” control signals select the W-Bus as the data source for normal register-write operations, and the S-Bus for increment/decrement operations.

The INC.MX0 microcode signal (1.B4) selects between increment and decrement functions, while /INH.INC will inhibit increment operations to stall PC when an interrupt is detected, for instance. Decrement operations are valid only for the low-order 8-bits and are used only on the 8-bit SP register.

Address Registers (PCL/PCH, DPL/DPH, SP, T)

The Address Registers (1.A-H7) are the Program Counter (PCL/PCH), the Data Pointer (DPL/DPH), the Stack Pointer (SP) and a Temporary Register (T). Each of these registers is mirrored by a corresponding shadow register in order to deliver register values to both the R-Bus and the internal address bus (ADL/ADH) efficiently. Asserting the /PCL.R control signal (1.B7) delivers the PCL register value to the R-Bus, whereas asserting /PCL.AD does the same to the internal address bus (ADL). PCL.WR clocks both PCL->R and its shadow register PCL->ADL at the same time to ensure their values are always identical.

PCL, PCH, DPL and SP take input values from either the W Bus or the S Bus, as specified by the corresponding “.WS” control signals. Since DPL is only ever incremented as an 8-Bit quantity, DPH does not need an S-Bus input. Instead, DPH may be loaded directly from memory through the “D->DPH” buffer (1.H6) by /DPH.LD. This path is required during indexed addressing to load the high-byte of an address from memory while the ALU and W-Bus are busy adjusting the low-byte.

Bus Hold ICs (R.HOLD, ADL.HOLD, ADH.HOLD)

Three 74ACT1071s bus-hold ICs (R.HOLD, ADL.HOLD and ADH.HOLD) are attached to the R, ADL and ADH busses respectively (1.D-F8). These are part of the bus management scheme that is used throughout the CPU to avoid bus contention during transitions. They are optional ICs, whose function is needed only to hold charge in the busses when the CPU is being single-stepped. They may be dispensed with during normal operation.

Address Bus (ADL/ADH, A-Bus)

The external address bus (A-Bus) is connected to the internal address bus (ADL/ADH) via two tri-state buffers (ADL.A and ADH.A). These are controlled asynchronously by the BE (Bus Enable) external control signal (with the BE pin on the 65C02 and the AEC pin on the 6510). 74AC541 parts should be used for these buffers if it is anticipated that the CPU will operate in a system which shares the CPU’s external address bus with other ICs. In such situations, the active drivers of the 74AC541 are required to charge the external address bus during Phase 2. Otherwise, the much faster (but passive) 74CBT3245 parts may be used for speed-critical applications.

R->DB Buffer

The “R->DB” 74AC541 buffer (1.E5) delivers register values from the R-Bus to the D-Bus during register store operations. It is enabled by the R/W control signal during PHI2 only (see bus management). The DPH+1 control signal will inhibit this buffer for special processing of “DPH+1” opcodes (see Undocumented Opcodes.)

Constant Generators (CGL, CGH)

CGL (1.A7) and CGH (1.I7) are constant generators. CGL is used during interrupt handling to generate the low-byte of the interrupt vector address. CGH provides the address high-byte for zero-page addressing ($00), for stack addressing ($01) and for interrupt vector addressing ($FF).

IR Register

The IR register (1.I6) holds the current Opcode. It is loaded directly from the D-Bus during SYNC cycles. The /INT.ON control signal has the effect of “loading” a BRK opcode into IR during interrupt processing.

Microcode ROMs

A pair of control ROMs on each CPU Card generates 16 Microcode Signals, which together determine the behaviour of the data path on that card. A given address in ROM holds a specific C74-6502 Microinstruction, and these are executed in sequence according to the Microcode.

Most Microcode signals pass through Microcode Decoders (see C74-6502 Decoder Values) which in turn generate specific datapath control signals. A few microcode signals, however, connect directly to the datapath. On Card A they are as follows:

- IR.LD (1.G3) — triggers IR.WR to load IR from memory during a fetch-opcode cycle.

- DPH.LD (1.H6, 1.H3) — used to load DPH directly from memory.

- INC.MX0 (1.A4) — selects between INC16 increment and decrement functions

Microcode Decoders

The C74-6502 uses a Vertical Microcode scheme, requiring Microcode Decoders to generate control signals. These decoders are labelled with the “.MX suffix”. On Card A they are as follows: R.MX, WR.MX, INC.MX and AD.MX. (See C74-6502 Decoder Values)

R.MX Decoder

The R.MX Decoder (1.F1) generates active-low datapath control signals to output-enable the various registers onto the R-Bus (e.g., “A.R” for the A Register). In addition, the decoder also includes several special signals as follows:

- SPI.EN — enables the built-in SPI interface on Card C

- CFG.R — output-enable the special CFG register on Card C (to configure the CPU)

- STP.EN — triggers 65C02 STP function on Card B

- A&X.R — output-enable A&X register on Card B (See A&X Undocumented Opcodes)

- BCG.R — output-enable Bitwise Constant Generator on Card B (for 65C02 operation)

AD.MX Decoder

The AD.MX Decoder (1.E1) selects address registers depending on the addressing mode in effect, as follows:

- PC.AD — Program Counter (PCH/PCL —> ADH/ADL)

- DP.AD — Data Pointer (DPH/DPL —> ADH/ADL)

- DPT.AD — Calculated Low-byte (DPH/T —> ADH/ADL)

- PBA.AD* — Previous Bus Address (ADL/AHD unchanged)

- ZPD.AD — Zero-Page (“$00”/DPL —> ADH/ADL)

- SP.AD — Stack Page (“$01”/SP —> ADH/ADL)

- FDP.AD — Interrupt Vector High (“$FF”/DPL —> ADH/ADL)

- FCP.AD — Interrupt Vector Low (“$FF”/CGL —> ADH/ADL)

*PBA Addressing supports 65C02 behaviour during Dead Cycles.

WR.MX Decoder

The WR.MX Decoder (1.G1) selects the target register for register write operations (e.g., “A.W” for the A register). In addition, the decoder also includes several special purpose control signals, as follows:

- AXS.W — indicates a write to X and S registers (see AXS Undocumented Opcode)

- P.W — indicates a write to the P register on Card B

- ML.W — triggers the 65C02 ML Pin logic on Card B

- WAI.EN — enables the WAI Opcode logic

- DPH+1 — DPH+1 Special Register on Card B (see H+1 Undocumented Opcodes)

- MEM.W — signals a write to memory, R/W Signal

“.W” control signals from the WR.MX Decoder pass through the WR-Latch flip-flops (1.G3) to control timing and clock registers precisely at the end of the cycle. WR-Latch is cleared mid-way through the cycle by the WR.CLR signal from the Monoflop circuit (1.I1). The Monoflop generates a brief low-going pulse at the fall of PHI11 (the pulse is as long as the propagation delay of three inverters in the Monoflop circuit, ca. 15ns for AC logic).

INC.MX Decoder

The INC.MX Decoder (1.H1) selects the address register that will receive the output of the 16-Bit Incrementer (INC16) from the S-Bus. (E.g., “PC.WS” to select the PC register)

The INC.MX0 Signal selects between increment and decrement functions, and the INC.MX1 and INC.MX2 Microcode Signals select the register where to store the result (PC, None, DPL, SP respectively). The INC.MX decoder selects a target register only. The input to the Incrementer is always the address on ADL/ADH. Note that the incrementer always operates on 8-Bits for DPL and SP, but a full 16-Bits for PC. DPL and SP share the same S-Bus datapath, which is possible because the microcode never requires DPL and SP to be manipulated at the same time.

R/W, SYNC Signals

The R/W Signal (1.D1) drives the R/W CPU Pin. The pin is driven low to indicate a cycle in which the CPU is writing to external memory. The MEM.W control signal triggers this write-to-memory condition. The DPH+1 control signal will also force a write to memory (used for H+1 Undocumented Opcodes). The RES.PND and RES.L control signals prevent R/W from going low during RESET.

The SYNC signal (1.D1) drives the SYNC CPU Pin. SYNC is high during any cycle in which the CPU is fetching an opcode from memory. The IR.LD Microcode Signal indicates a write to the instruction register, and signals a fetch-opcode cycle.

Bus Management

The C74-6502 implements a bus management scheme to avoid transient collisions when a shared bus transitions from one driver to another. Timing on the busses is arranged such that drivers are enabled only during half the cycle. In this way no driver will be active when a new driver is enabled, and therefore the bus is always free of collisions. Under normal operation, bus capacitance maintains data values on the bus when drivers are inactive. Bus Hold ICs are required if the CPU will be single-stepped since the busses will drain over time.

Specific provisions of this scheme include:

- All drivers on the W-Bus are enabled during Phase 2 only

- All drivers on the R-Bus are enabled during Phase 1 only

- All drivers on the ADL/ADH are enabled during Phase 1 only*

- All drivers on the B-Bus (on Card B) are enabled during Phase 1 only

- The P Register (on Card B) drives the R-Bus during Phase 1 only

- Bus Hold ICs maintain values on the R, ADL, ADH and B busses

- The W-Bus does not require bus-hold since it’s values are registered at the end of Phase 2

See here for further details.

*NOTE: Driving the Address bus during phase 1 only made the CPU incompatible with computers like the Commodore 64 where the CPU and the VIC chip share the Address bus in alternate phases of the clock. This problem had to be patched in the prototype boards to correct it (See Patch #5 in C74-6502 PCB Patch Guide).

6510 Port

The 6510 Port is an on-board 6-bit bi-directional I/O port. It is mapped to addresses $0000 and $0001 for compatibility with the MOS 6510 Microprocessor. On the C74-6502, the 6510 port intercepts the Internal Data Bus (D-Bus) before it reaches the External Data Bus (DB). The “D->DB” bus transceiver (2.H4) performs this function. The 6510 port therefore overrides external components mapped to these addresses.

Address Detector/Decoder

The Address Detector circuit (2.A2) triggers the PB.CS signal to enable the port when either $0000 or $0001 appears on the address bus. The 816BNK0 control signal is used to manage the mapping of the port to one or all of the 64k memory banks that are available in the address space when the Card C K24 logic is active. As with other write-enable signals in the CPU, both the DDR.W and PDR.W signals are captured by WR.LATCH flip-flops (2.A7) to manage timing.

6510 Port Registers

The port registers are the Data Direction Register DDR (2.D2), the Port Data Register PDR (2.G2), and the Port Output Data register POD (2.F2). The DDR configures the port’s bits for either input or output — each bit in the DDR enables a corresponding input or output tristate buffer (2.C5-E6) for the port data lines. A high DDR bit indicates output for the selected port pin.

The PDR input is sampled on the rising edge of PHI2. When working as output, the port pins will reflect immediately any value written to the POD by the CPU. A read of the port by the CPU will reflect the value held in the POD for any bit configured as output. PB6 and PB7 are pulled to ground, which means that port values read by the CPU will always have zeroes in the upper two bits.

Data Bus Buffer

The Data Bus Buffer (2.H4) links the CPU’s internal data bus (“D-Bus”) to the physical pins on the external data bus of the CPU (“DB”).

Pinout Headers

Two distinct header formats exist, one compatible with the 6502/65C02 pinout and the other with the 6510 pinout (2.F9). The latter includes the 6510 port pins. In both cases, low-value series resistors connect internal circuitry to these external pins. This is in order to reduce cross-talk and improve signal integrity should an external ribbon-cable connector be used on the headers. Details on how to configure the headers is available on the CPU Datasheet.

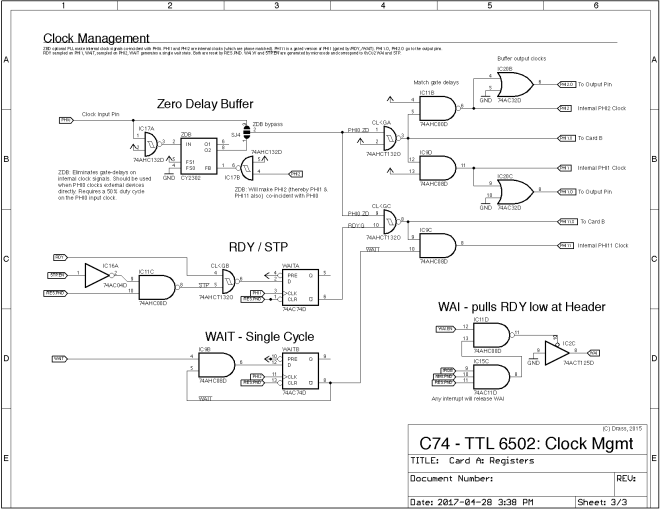

Clock Management Logic

The Clock Management circuitry of the C74-6502 is responsible for generating internal clock signals, and implementing various wait-state mechanisms, including RDY, WAI, STP and WAIT (WAIT is used to support two-cycle CMOS Decimal Mode operations).

The input clock signal is labelled PHI0, which in turn is used to generate PHI1, PHI2 and PHI11. PHI1 and PHI2 are free-running clocks, whereas PHI11 is a gated version of PHI1 (meaning that it will be paused by the various wait signals). PHI11 is the CPU’s main internal clock. Note that the PHI0 input clock signal may be optionally routed through the Zero Delay Buffer (ZDB) (3.B2). This is in order to eliminate the propagation delay associated with the clock management logic at high clock-rates. (See ZDB Forum Post).

PHI1.X, PHI11.X and PHI2.X are inter-card clock signals. They travel to the other CPU cards via inter-card connectors where they are used to derive synchronized card-local signals. PHI1.O and PHI2.O are buffered clocks output to the corresponding external CPU pins.